中国企业报集团主管主办

中国企业信息交流平台

2024年是至强的大年。

先于6月正式发布的至强® 6700E系列开启了全新的、更为简洁命名方式:至强® 6能效核。144核的规格也意味着英特尔在最近几年当中首次在核心数量方面实现了领先。而且,这还并不是至强6的最强形态,毕竟大家都知道还有个6900P系列嘛。

9月26日,至强6这个“最强形态”终于正式发布,主要规格非常震撼。即使面对今年内晚于自己发布的其他厂商同级别CPU,至强® 6900P的已有规格也战力十足。

最强至强能有多强?

英特尔代号Birch Stream的新一代服务器平台所采用的至强6处理器是分批次发布的。6月发布的是代号Sierra Forest的能效核处理器6700E系列(E后缀即Efficiency Core,能效核的标记),目前发布的是代号Granite Rapids的性能核6900P系列。今年底和明年初还会陆续发布6900E、6700P,以及6500/6300等。未来的Intel 18A制造工艺的处理器,如Clearwater Forest,也会继续用于Birch Stream平台。

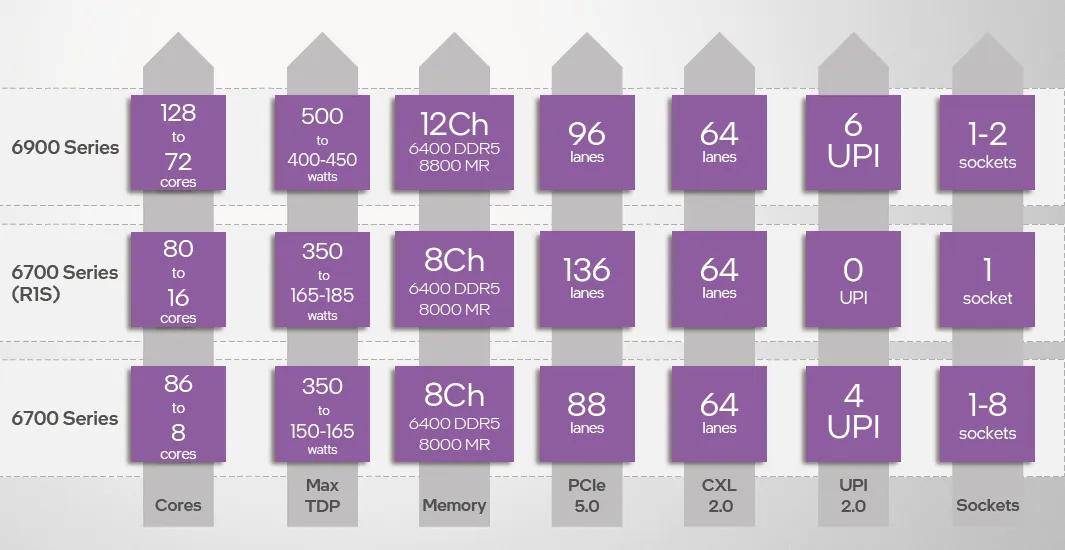

至强6900P是英特尔专为计算密集型工作负载设计的处理器,也是Granite Rapids的“完全体”。后缀的“P”意味其采用的是Performance Core,即性能核,规模大、性能强;6900的数字型号则说明其核心配置拉满——提供了72到128核的多种规格,TDP有400W和500W两种,组合成已公开5种型号,显得比较简洁。当然,依照惯例,云厂商等大客户还会有若干定制型号的。单就内核数量而言,6900P系列相对前两代“Rapids”产品线顶配的56/60(Sapphire Rapids)或64核(Emerald Rapids)直接翻倍!如此巨大的迭代幅度非常罕见,也难怪英特尔要改命名方式了,由表及里都透着一个意思:厚积薄发、脱胎换骨!

尤为值得一提的是:至强6900P也是业内首款性能核数量正式“破百”的产品,其他同级产品,不论是x86架构还是Arm架构都只达到了96核的水平。它们的性能核数量要追平英特尔,起码得等到下个季度。

随着内核规模增加,至强6900P的L3缓存达到了504MB。为了配合倍增的核数和显著提升的算力,至强6900系列的存力也大为增强,内存带宽方面不仅支持12通道DDR5 6400;并引入了新型内存MR DIMM,把数据率大幅提升至8800MT/s,基本内存带宽可以达到第五代至强可扩展处理器的2.3倍。另外,至强6还支持CXL 2.0,尤其是包括Type 3设备(也就是CXL内存),可以进一步扩展内存容量和带宽。

至强6900P的UPI2.0链路也有很大改进,速率提升到24GT/s,数量增加至6条,使得双路互联效率进一步提升。结合内核数量、内存带宽等方面的全面提升,至强6900P可以被视作高算力+高存力平台的最强机头,不论是科学计算,还是AI集群。根据已透露的测试,至强6900P平台的数据库、科学计算等关键应用负载的表现是上一代产品的2.31倍-2.5倍,AI应用性能是其1.83倍-2.4倍不等。

至强6的扩展能力也有不小的提升。其中6900系列单插座不论是性能核还是能效核均可提供96通道PCIe 5.0,双路即可提供192通道PCIe 5.0。未来上市的6700系列单路型号可以提供136通道PCIe 5.0,双/多路型号单插槽也可以提供88通道。相较而言,第四、五代至强可扩展处理器的PCIe 5.0通道数量为80。CXL支持能力方面,至强6 6900、6700系列都支持64通道CXL 2.0。

更多的内核、更多的内存通道、更多的PCIe通道需要更大规模的插座接口支持。 至强6带来了两种接口:LGA 4710和LGA 7529。至强6900系列使用面积较大的LGA 7529插座,提供最强大的内存带宽和扩展能力,是未来高性能、高密度服务器的基础。至强6700以及未来的6500/6300系列使用LGA 4710,尺寸与第四、五代至强的LGA 4677相仿,内存、PCIe的通道数相同或相近,有利于主流服务器内部布局习惯的延续性。

改进的EUV:Intel 3

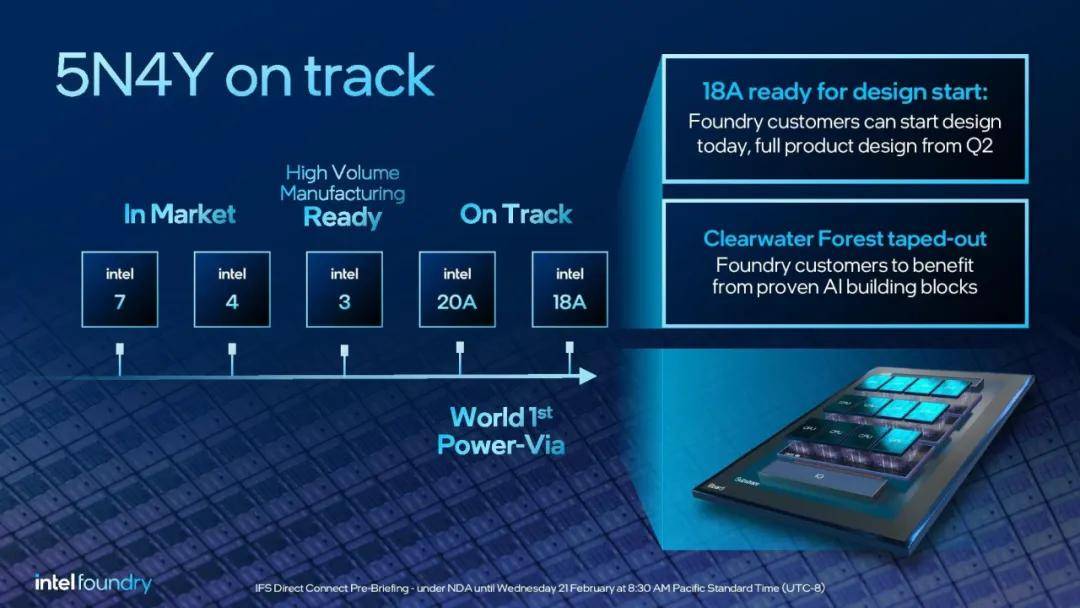

核心规模的飙升首先得益于至强产品线终于获得EUV光刻机的加持。在2023年发布的酷睿Ultra已经率先使用了引入EUV的Intel 4制造工艺。而2024年发布的至强6则使用了进一步改良的Intel 3制造工艺。

2021年7月,英特尔CEO帕特·基尔辛格公布了“四年五个制程节点”(5N4Y)的工艺路线图。Intel 3的量产时间节点位于2023年底,节奏基本符合计划。从基于Intel 4制造工艺的酷睿Ultra的市场表现看,EUV的加持确实明显提升了英特尔处理器的竞争力。至强6所采用的Intel 3制造工艺相对Intel 4可以规划更多的金属层、拥有更多细分版本。

Intel 3在更多的步骤中应用EUV光刻,可以提供更密集的设计库、更高的晶体管驱动电流。Intel 3还有三种变体,包括3-T、3-E和3-PT。Intel 3、3-T是基本工艺,主要用于CPU;3-E是功能扩展;三者都支持TSV;Intel 3的这三种变体与Intel 4相比可以提升18%的性能功耗比。而3-PT进一步增加混合键合的支持能力,带来了更高的性能并且易于使用。Intel 3所有四种节点变体都支持240 nm高性能和210 nm高密度库,而Intel 4只支持240 nm高性能库。

对于性能取向,Intel 3针对高性能运算进行优化,可以支持低电压(<0.65V)和高压(>1.3V)运行,且在各电压下的频率均高于Intel 4。

微架构大迭代

至强6900P采用的性能核微架构代号Redwood Cove。Redwood Cove也是近年来英特尔最重要的微架构迭代,不但给服务器产品线带来了新名字,在消费类产品线同样开启了新的命名序列酷睿Ultra。

我们先快速回顾一下Redwood Cove的上一代Golden Cove/ Raptor Cove。Golden Cove其实也是非常重要的迭代,在消费类开启了大小核时代(第12代酷睿处理器),在服务器上就是第四代至强可扩展处理器。Golden Cove相对其前代的微架构大幅度提升了前端:

指令TLB翻倍,从128条增加到256条;

指令提取带宽从每周期16字节翻倍到32字节;

解码器从4路扩展到6路;

微操作缓存从2304条增加到4096条;

其他L1 BTB、L2 BTB等也有所提升。

Golden Cove的后端当然也有提升,譬如重排序缓冲区、分支目标缓冲区也有大概30%左右的提升,只是相对前端幅度不那么大。

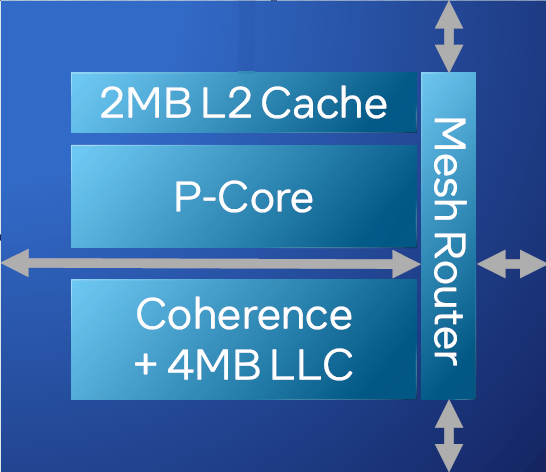

Raptor Cove的微架构与Golden Cove差异不大,表现在实际产品上主要是缓存的提升,如基于Raptor Coved的第13代酷睿(Raptor Lake)的每核心L2缓存从12代(Alder Lake)的1.25MB提升到2MB;第五代至强可扩展处理器(Emerald Rapids)和第四代(Sapphire Rapids)每个核心的L2缓存都是2MB,但前者每个网格的末级缓存(Last Level Cache,也可继续俗称为L3缓存)从后者的1.875MB猛增到5MB。

Redwood Cove相对Golden Cove/ Raptor Cove的最重要变化是:

指令缓存从32KB增加到了16路、64KB;

微操作队列从144个条目增加到192个条目;

指令执行延迟降低;

更智能的预取和改进的BPU;

L2缓存的带宽有所提升;

AMX增加FP16支持。

当然,Redwood Cove还有一个重大的优势就是“命好”,也就是前面提到的EUV制造工艺。但即使有革命性的制造工艺加持,至强6性能核也没过分扩张每个内核的规模。就至强6性能核的内核而言,每个网格节点是一个P核,每个P核配置私有的2MB L2缓存,以及共享的4MB 末级缓存。虽然平均到每个核的缓存容量并不比上一代至强(Emerald Rapids)多,但胜在总核数翻倍后。至强6性能核每个处理器可共享的末级缓存总容量依旧达到504MB,远超第五代的320MB和第四代的112.5MB。

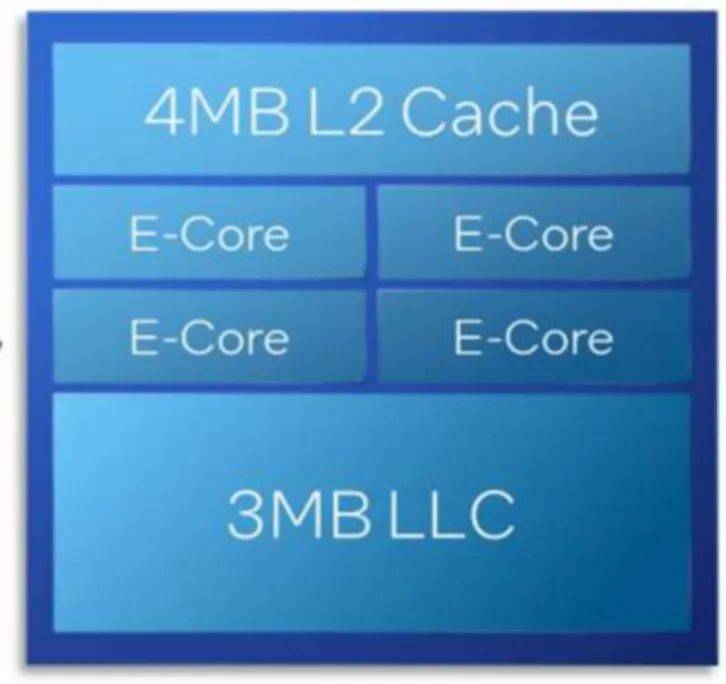

在此也顺便提一下至强6能效核的微架构Crestmont。这个微架构同样出现在了酷睿Ultra的能效核当中。Crestmont是2或4个内核为一组共享L2缓存。在至强6能效核当中,每2或4个内核与4MB的L2缓存(在酷睿Ultra中则为2MB)构成一个模块,这几个内核共享频率和电压域。这个模块对应的网格还拥有可整个处理器全部内核共享的3MB的末级缓存。换句话说,虽然至强6能效核的核数更多,但实际上网格规模比至强6性能核小。

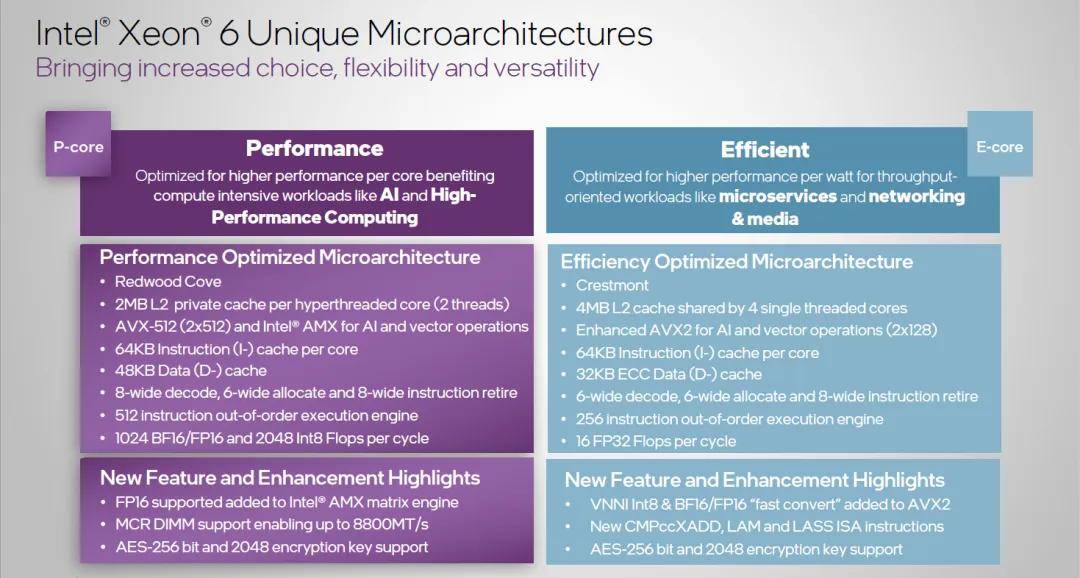

能效核的指令缓存与性能核都是64KB,但数据缓存分别是32KB和48KB。前端的指令解码器宽度也有差异,分别为6和8宽。指令乱序执行引擎差异较大,能效核是256条而性能核是512条。能效核不支持性能核所支持的AVX-512和AMX,这也可以明显减小矢量运算单元的晶体管占用,但代价是每周期的单精度浮点运算次数有了数量级的差异。但能效核也改进了AVX2,增加了VNNI的INT8和BF16/FP16快速转换,这样在处理AI应用的时候表现也还有所改善。另外,其256位加密和1024/2048密钥也获得了能效核的支持,确保至强6平台的安全水平基本一致。

缓存规模、前端宽度以及矢量单元的差异,使得至强6性能核和能效核有不同的定位。早先发布的至强6能效核更适合微服务等运算强度相对较轻,可在高核心数量和规模扩展方面收益的任务,以追求更高的能效、更高的机架利用率。而现在发布的至强6性能核更适合大数据、建模仿真等计算密集型和人工智能任务,为高性能优化,单颗处理器的功耗直飚500W——当然,跟同期发布的Gaudi AI加速器的新品或类似的加速器产品相比,能耗是应有的代价,有能力提升性能上限才是正经事。

内存性能大跃进

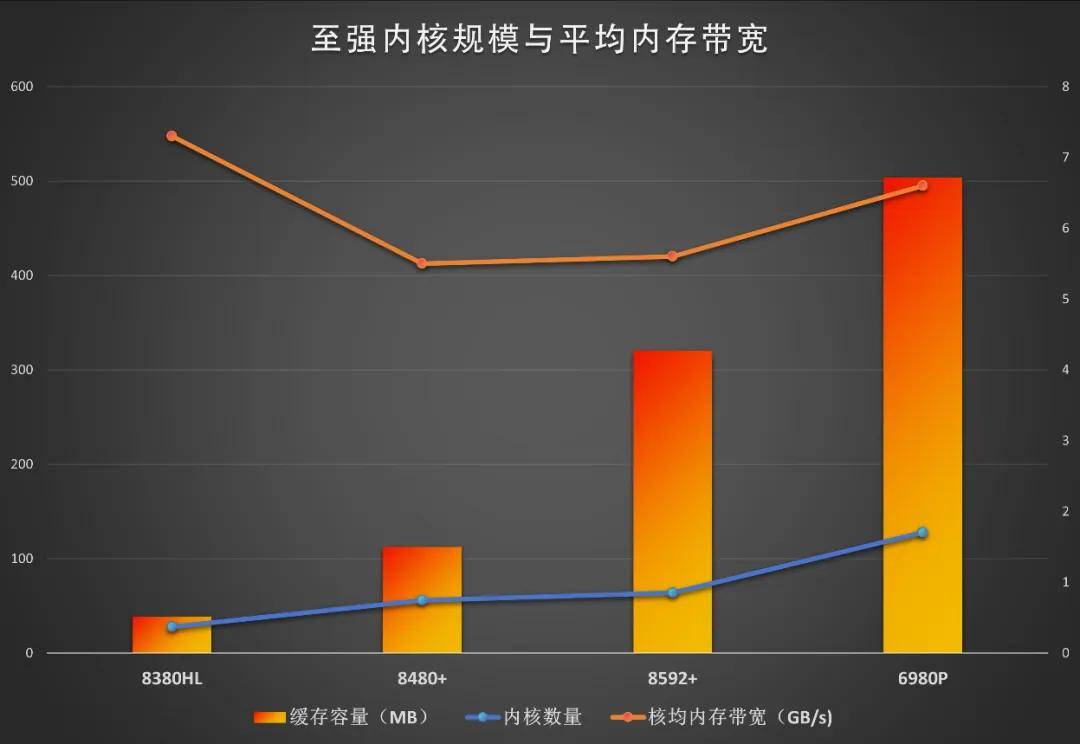

内存(DRAM)的数据存储依赖电容,这个特点使其微缩和提速的难度大于晶体管。因此内存并没有沾摩尔定律的光,带宽和密度的增长落后于CPU、GPU的发展。内存带宽滞后于CPU内核数量的增长导致一个长期问题:平均每个内核的内存带宽增长乏力,甚至出现倒退。譬如第三代至强可扩展处理器内核数28,内存是八通道DDR4 3200,理论上的内存总带宽为205GB/s,平均每核7.3GB/s;四代是56或60核,内存八通道DDR5 4800,总带宽307GB/s,平均每核5.5GB/s;五代提升到DDR5 5600,内核再增加到64,平均带宽改进甚微。第四、五代至强可扩展处理器虽然引入了新一代的DDR5内存,但由于内核数量相对三代翻倍,内存带宽的增长幅度还是跟不上。同时期其他厂商的CPU核数在屡屡跃进的过程当中也存在同样的问题。为了弥补内存带宽增长较慢的问题,第四代至强可扩展处理器给部分用于科学计算的型号引入了HBM,五代则大幅度增加了末级缓存的容量,并支持CXL 2.0内存扩展。

在至强6900P上,内存问题终于得到了比较好的解决。这涉及三个角度:

1.大容量末级缓存。前面提到过,6900P每个网格提供4MB L3,总容量达到了504MB,分别是四代的4.5倍、五代的1.6倍。而且,至强的全网格架构使得任意内核访问末级缓存的延迟相比其他厂商的一些产品有更优的表现,例如不需要跨计算单元而造成延迟剧增。这种架构效率更高的优势也是至强在核数曾落后的情况下还能打的有来有往的关键原因。

2.DDR5内存双管齐下提升带宽。至强6900系列支持12通道DDR5 6400,总带宽可以达到614GB/s,平均每核的带宽大致还有5GB/s的水平。6900P还支持新型内存MRDIMM,频率提升至8800MT/s,总带宽达到了845GB/s,平均每核6.6GB/s,也明显超过了前两代产品,大幅度逆转了内核数量增加、平均内存带宽不升反降的问题。

MR(Multiplexed Rank)DIMM打开了DDR内存性能提升的新方向。DRAM通常由1到2个Rank组成,每个Rank的位宽为64位,如果考虑ECC,那就会有72或80位,但有效的数据是64位。消费类内存(UDIMM)可能只有1个Rank(颗粒数量较少的情况下),但追求大容量的服务器内存(RDIMM)基本上都至少有2个Rank。在以往的内存模式当中,一次只读取一个Rank的数据,另一个Rank暂时闲置时可以做刷新操作,以保持数据——这种轮流读取、刷新Rank的特点延续了多年。MRDIMM设计了一个数据缓冲区,通过将两个内存Rank分别读入这个缓冲区,再从缓冲区一次性传输到CPU的内存控制器,由此实现了带宽翻倍。第一代DDR5 MRDIMM的目标速率为8800 MT/s,其实每个Rank只相当于4400MT/s。现在DDR5 6400已经开始普及,因此MR DIMM的第二阶段目标是达到12800 MT/s,预计在2030年代的三代会提升至17600 MT/s。

3.CXL 内存扩展。第四代至强可扩展处理器开始引入CXL支持,当时是1.1版本,暂时也没有公开支持Type 3设备(也就是CXL内存)。从第五代开始正式引入了CXL 2.0,包括Type 3,可以帮助扩展内存容量和带宽。在至强6上,CXL设备的应用将更为普及,关键的CXL2.0标准设备,以及后向兼容的CXL1.1设备,预计都会陆续涌现。

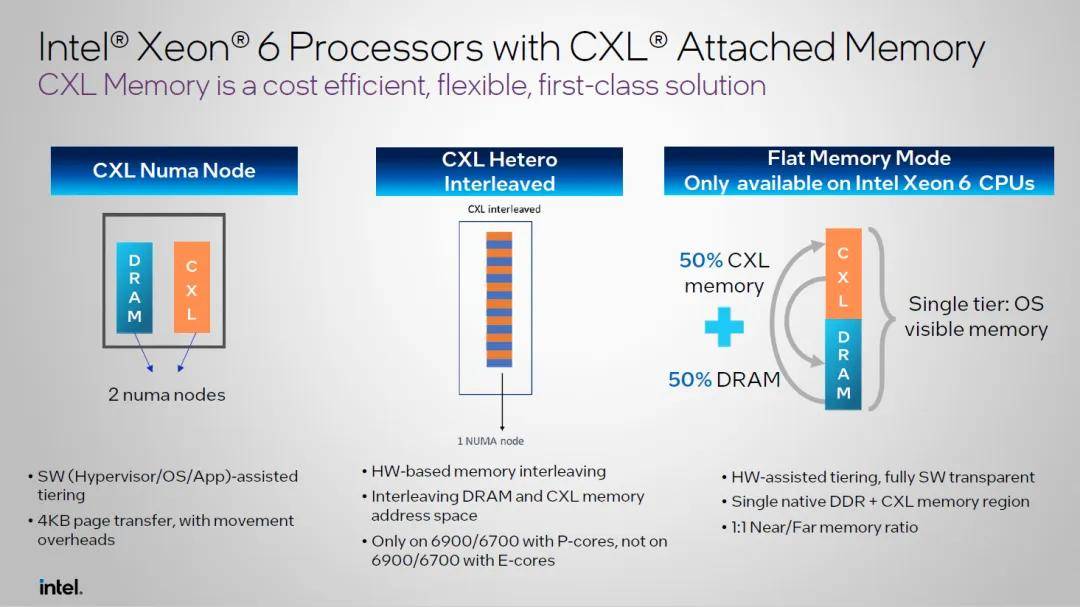

这里重点说一下CXL内存的优势。CXL2.0支持链路分叉,使一个主机端口可以对接多个设备,而且提供更强的CXL内存分层支持,可实现容量和带宽扩展。至强6支持3种CXL内存扩展模式:CXL Numa Node、CXL Hetero Interleaved、Flat Memory。

在CXL Numa Node模式下,系统的标准内存和CXL扩展内存被视为两个独立的Numa节点进行控制。每个Numa节点都有自己的内存地址空间,系统软件或应用程序可以将任务分配到不同的Numa节点,从而优化内存的使用。CXL Numa Node模式适用于需要精细内存管理的应用,可以通过操作系统、虚拟机管理程序(Hypervisor)或应用程序本身来辅助分层管理内存。

Hetero Interleaved(异构交织)模式通过将系统的标准内存和CXL内存混合在一起,形成一个统一的Numa节点。每个内存地址空间中的数据可以交替存储在DRAM和CXL内存中,从而均衡内存带宽,减少延迟。异构交织模式适用于对内存带宽有高需求的应用,特别是当需要将DRAM和CXL内存结合使用时。此模式只有在配备性能核的至强6700P、6900P上才支持。假设将每颗至强6900P的64通道CXL用满,可以额外增加256GB/s的内存带宽,单处理器就可以实现TB级的内存带宽,还是相当可观的。

Flat Memory(平面内存)模式下,CXL内存和标准内存被视为单一的内存层,操作系统可以直接访问统一的内存地址空间。硬件辅助的分层管理可以确保常用数据优先存储在标准内存中,次要数据存储在CXL内存中,从而最大限度地提升内存使用效率。平面内存模式最大的价值在于无需修改软件即可利用CXL内存扩展,而且这种模式适用于所有的至强6处理器。但平面内存模式要求标准内存和CXL内存是1:1配置,这略为限制了硬件采办、升级的灵活性。整体而言,平面内存模式是至强6时期最易用、收效最直观的模式,有望成为CXL内存扩展的主要模式。

踏上Chiplet异构之路

至强6是至强家族首次将计算和IO芯片独立,再通过Chiplet形式封装在一起,总算是把高级封装的优势真正发挥出来了。

第四代至强可扩展处理器是英特尔的首个Chiplet设计的至强处理器。其XCC版本内部是4颗芯片通过10组EMIB对等连接,每颗芯片提供15个内核、2通道内存控制器、1组加速单元,以及UPI、PCIe PHY若干。另外,还可以通过EMIB封装4颗HBM。

第五代至强可扩展处理器使用2颗芯片封装而成,所使用的EMIB数量明显减少,相应地也节约了芯片面积。虽然内核数量略有增加,但也损失了UPI、PCIe的数量,也不再能够搭配HBM。

随着制造工艺演进,偏重计算性能和晶体管密度的处理器内核,与偏重高速信号互联的IO控制器对制造工艺的要求产生了差异,因此,典型的Chiplet设计将计算和IO分离,分别应用不同的制造工艺。英特尔在14代酷睿上便采用了这种方式,分为Compute Tile、SoC Tile、IO Tile、Graphic Tile。代号Ponte Vecchio的英特尔Data Center GPU Max利用Foveros和EMIB技术,将47个小芯片封装在一起,包括Compute Die、Base Die、Rambo、IO Die等。

至强6终于也拆分成计算单元(Compute Tile)和IO单元(IO Tile),分别由Intel 3和Intel 7工艺制造。

计算单元

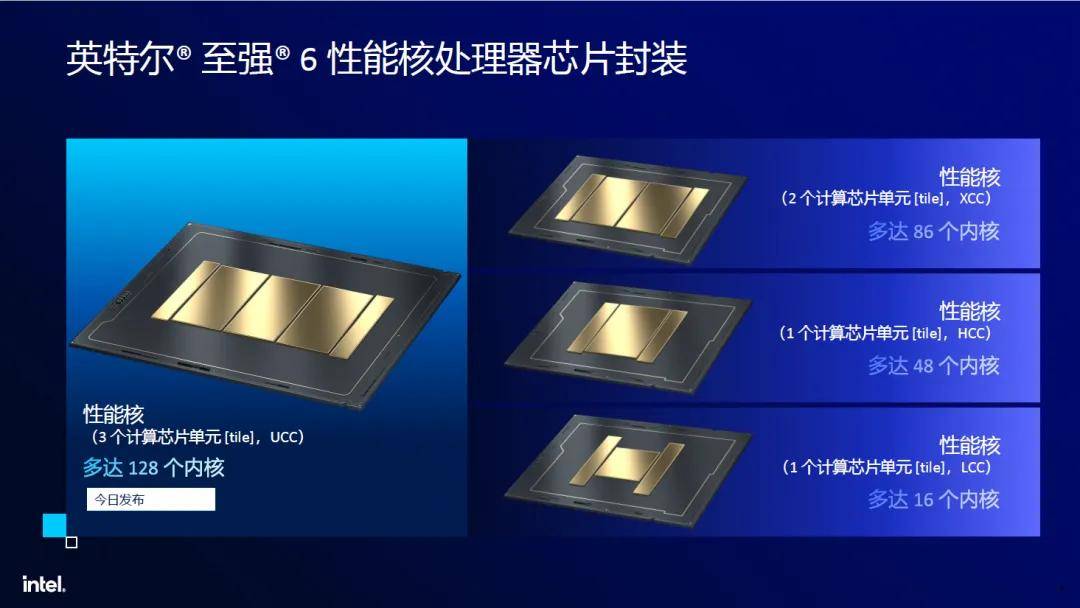

根据收集到的信息,对于能效核,目前只出现了一种计算单元的设计,每个单元最多提供144个内核、4组内存控制器共八通道;对于性能核,则是有三种计算单元的设计,可分别用于组合高核数、中等核数、低核数的规格。

至强6900P使用了三个计算单元,每个单元43个内核、两个内存控制器,总共构成129个内核(只使用128个)和12个内存通道。这种计算单元姑且称之为单元A,三个单元A构成的处理器被称为UCC。

未来发布的6700P核数跨度会很大,其中单路型号规划为16~80核,多路型号为8~86核。单元A有4个内存通道,两个单元A组合可以提供最高86核,下限应该不低于48核(否则屏蔽的内核数量就实在太多,也太浪费EMIB成本),这种规模的处理器被称为XCC。48核以下的中等核数被称为HCC,使用一种专门开发的单元B,每个单元提供48个内核和4个内存控制器。HCC核数的下限预计在24核左右。8和16核的6700P被称为LCC,需要使用第三种单元C,16个内核和4个内存控制器。

通过使用3种计算单元进行组合,至强6性能核可以构建跨度从8~128核的、非常绵密的规格。也许会有人认为,相比其他厂商只用一种规格计算单元实现扩展的设计,英特尔需要设计三颗不同的芯片的成本会更高。但我认为,这是英特尔优先考虑性能的结果。首先,至强6将内存控制器安排在计算单元中,离内核更近,延迟更低,即使因此牺牲了单元组合使用的灵活性也是值得的。其次,至强6性能核给不同规模的内核数量规划不同的网格规模,有利于降低核间的延迟,甚至,有可能LCC会针对较低的核数改用环形总线。综上,预计至强6性能核相对同等规模的其他厂商的产品依旧可能会拥有内存延迟低、缓存延迟低的优势。

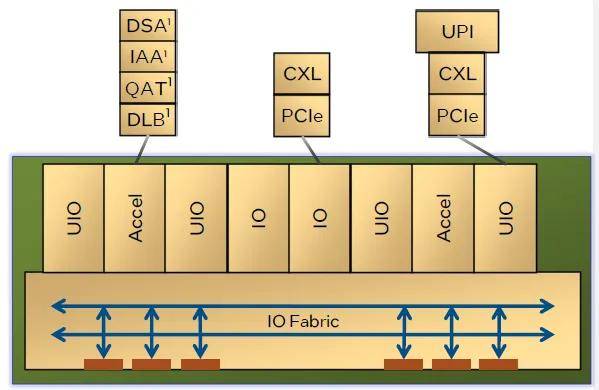

IO单元

IO单元方面,至强6900、6700系列都使用2颗相同的IO芯片。每个IO芯片由2个IO模块、4个UIO模块、2个加速器模块,以及IO网络接口构成。每个IO模块提供x16 PCIe或CXL连接;每个UIO模块提供x24 UPI2.0,或复用为x16的PCIe或CXL;每个加速器模块提供DSA、IAA、QAT、DLB加速器各一个。

以这次发布的至强6900P为例,两个IO单元总共提供8个UIO和4个IO模块。其中6组UIO负责提供6个UPI2.0互连,剩余的2个UIO和4个IO模块正好提供6×16=96通道的PCIe 5.0。双路至强6900P的UPI不但速率高(24GT/s,高于五代的20GT/s和四代的16GT/s),连接数量也提升了50%。

对于还未发布、也是主力产品的至强6700系列,估计由于要使用规模较小的插座,只提供最多4组UPI用于多路的互联,PCIe通道也有所缩减。但即使如此,至强6700系列的单路型号在将所有UIO配置为PCIe之后,单插槽就可以提供多达136个PCIe通道,或64通道CXL。如果用单路至强6700配合半宽主板构建双节点服务器,那一个机箱内的PCIe/CXL扩展能力(272 /128)远远超过已知的任何双路服务器。这种机箱可能会成为新的池化形态,可以更高的密度提供NVMe存储、CXL内存、加速器等。

结 语

由于英特尔在14nm到10nm制造工艺的迭代过程遇到了一些问题,以致此前几代至强平台在“核战”(比拼核数)中略显被动,但这个局面在至强6上有望完全逆转。改良后的EUV制造工艺看来没有束缚至强6的实力,核心数量、缓存容量、内存带宽等关键指标全都进入领先行列,一句话总结就是算力和存力的表现全部拉满。至强6900P系列在各种项目的测试当中,其代际性能提升就都是以倍数计,而非百分之十几、几十的进步。这种形势也使得英特尔得以全面竞争科学计算、大数据、AI等领域的性能王座。

此外,至强6终于实现计算与IO的解耦,也让至强6及未来的产品线走上了正确、灵活的道路,得以充分发挥Chiplet的优势。将Chiplet视作降低成本、提高良率的手段是狭隘的。Chiplet的价值在于灵活、复用、重构。英特尔长期以来很注重细分市场的耕耘,产品线非常复杂,正确利用Chiplet可以达到事半功倍的效果。我们非常期待至强6后续产品的陆续发布能够给业界带来什么样的想象力。

相关稿件